## Reduction of gate leakage current of HfSiON dielectrics through enhanced phonon-energy coupling

Chandan B. Samantaray and Zhi Chen<sup>a)</sup>

Department of Electrical and Computer Engineering, University of Kentucky, Lexington, Kentucky 40506 and Center for Nanoscience and Engineering, University of Kentucky, Lexington, Kentucky 40506

(Received 30 March 2006; accepted 2 September 2006; published online 17 October 2006)

The authors have investigated the effect of phonon-energy-coupling enhancement induced by rapid thermal processing (RTP) and deuterium annealing on the leakage current characteristics of HfSiON gate dielectrics. The leakage current is reduced by one- and-a-half orders of magnitude after RTP and deuterium annealing of HfSiON gate dielectrics. The leakage current density of the HfSiON gate insulator with equivalent oxide thickness of 5.2 Å was only  $4 \times 10^{-2}$  A cm<sup>-2</sup>. This suggests that HfSiON with the enhanced phonon-energy coupling can be scaled down to below 5 Å. © 2006 American Institute of Physics. [DOI: 10.1063/1.2363139]

The aggressive scaling and low gate leakage current are required to improve the current drive capability and to reduce standby power in future metal-oxide-semiconductor field effect transistors (MOSFETs).<sup>1</sup> For the above purpose, high-k gate dielectrics are extensively studied for the potential replacement of  $SiO_2$  and  $SiO_xN_y$  in advanced MOSFETs. One of the most promising high-k gate oxides is HfSiON due to its excellent thermal stability, improved electrical properties, and reduced dopant diffuson.<sup>2-4</sup> Recently, we discovered phonon-energy-coupling enhancement (PECE) effect of the SiO<sub>2</sub>/Si system, i.e., phonon-energy coupling is enhanced among Si-O, Si-Si, and Si-D bonds, leading to a large reduction of leakage current of SiO<sub>2</sub>.<sup>5,6</sup> The dramatic reduction of gate leakage current by five orders of magnitude was achieved by rapid thermal processing (RTP) and deuterium annealing of 2.2 nm SiO<sub>2</sub>. <sup>5,6</sup> This improvement was suggested to be caused by strengthening Si-O bonds due to enhanced phonon-energy coupling between Si-O and Si-Si bonds.<sup>6,7</sup> On considering the fact that Si–O and Si–Si bonds exist in HfSiON, it is expected that the RTP and deuterium processing of HfSiON may also improve its gate leakage current. In this letter, we report the leakage current reduction of HfSiON using PECE effect and its scalability down to 5 Å.

The *p*-type Si (100) substrates were cleaned by Radio Corporation of American (RCA) cleaning with NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O and HCl:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O followed by etching in a diluted HF (30:1) solution to remove native oxide and contaminations. The HfSiON films were deposited on the Si wafers by cosputtering (AJA International, ATC 2000 sputtering system) of Hf and Si targets in the presence of Ar, O<sub>2</sub>, and N<sub>2</sub> gases.<sup>8</sup> These films were submitted to different RTP sequences in N<sub>2</sub> flow at different temperatures (900–1100 °C) and time intervals (30–60 s). Also, we prepared control samples without any RTP treatments. The physical thicknesses of HfSiON layers were measured using ellipsometry. The compositions of the films were determined using x-ray photoelectron spectroscopy analysis. Al metal gates of 1000 Å thickness were deposited using thermal evaporation system (EDWARDS AUTO 306) through patterns of  $7.85 \times 10^{-5}$  cm<sup>2</sup> made by standard photolithography using SU-8 photoresist. Evaporated aluminum was also used for back side metallization. The final sintering was done at 450 °C in deuterium gas for 30 min. Electrical characterizations of the deposited gate dielectrics were performed using current-voltage (I-V) and capacitance-voltage (C-V) measurements. An Agilent 4155 B semiconductor parameter analyzer was used for I-V analysis and Keithley 590 CV for the C-V characterizations at 100 kHz and 1 MHz. Equivalent oxide thicknesses (EOTs) for HfSiON films in between 5.2 and 12.3 Å were extracted.

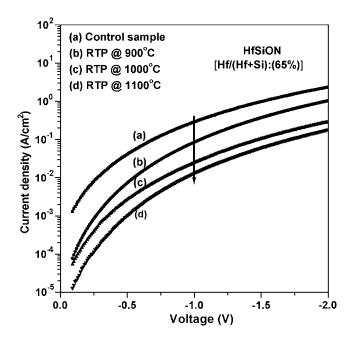

The leakage current characteristics for both control and RTP-annealed HfSiON with EOT of 12.3 Å are shown in Fig. 1. There is a large reduction of leakage current density (one- and-a-half orders of magnitude) for RTP-annealed sample at 1100 °C for 1 min, compared with that of the control sample. Further, it should be noticed that the leakage current also decreases by an order of magnitude for different annealing temperatures varying from 900 to 1100 °C. This

FIG. 1. Gate leakage current density vs gate voltages for control and rapid thermal annealed HfSiON [Hf/(Hf+Si): 65%] samples at different temperatures ranging from 900 to 1100 °C for 1 min in N<sub>2</sub> ambient.

0003-6951/2006/89(16)/162903/3/\$23.00

89. 162903-1

Downloaded 18 Oct 2006 to 128.163.42.72. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

<sup>&</sup>lt;sup>a)</sup>Electronic mail: zhichen@engr.uky.edu

<sup>© 2006</sup> American Institute of Physics

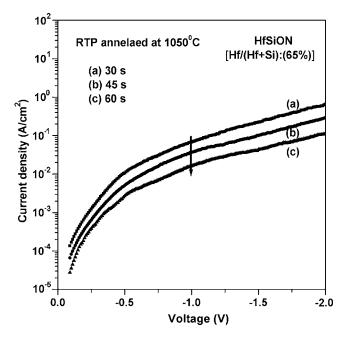

FIG. 2. Variation of leakage with voltage for HfSiON samples for different annealing durations varying from 30 to 60 s in N2 at 1050 °C.

improvement in leakage current is attributed to the enhanced phonon-energy coupling.<sup>5,6</sup> In our experiments, we measured the physical thickness of HfSiON samples using ellipsometry before and after RTP and found that it remained the same after high temperature RTP processing. Our results of the PECE effect on SiO<sub>2</sub> also showed that there is no thickness change for SiO<sub>2</sub> after RTP.<sup>6</sup> Thus, the leakage current density measured for HfSiON is not due to the increase in film thickness after RTP, but the strengthened Si-O bonds.<sup>b</sup> In addition, the leakage current characteristics of HfSiON with different annealing times were also measured as shown Fig. 2. The leakage current of the sample processed in RTP for 60 s at 1050 °C was  $7 \times 10^{-2}$  A/cm<sup>2</sup> at  $V_G - V_{FB} = -1$  V, lower than that processed in RTP for 30 s  $(4.3 \times 10^{-1} \text{ A/cm}^2)$ . Therefore, RTP processing for 60 s may enhance the film quality of HfSiON films, probably due to the optimized processing parameters.

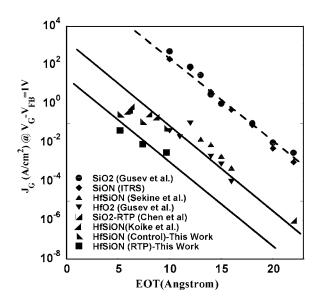

The leakage current of the HfSiON films as a function of EOT is shown in Fig. 3. The data show a reduction of leakage current by five orders of magnitude for HfSiON with PECE effect added, comparing to that of untreated silicon oxynitride. The leakage current is also one order smaller than other reported results of HfSiON and HfO<sub>2</sub>.<sup>8-10</sup> Koike et al. reported the lowest EOT of 6.0 Å estimated for HfSiON [Hf/(Hf+Si):80%], which is applicable to 45 and even 32 nm node high performances Si large scale integrations.<sup>8</sup> We report here a leakage current of  $2.8 \times 10^{-1} \text{ A/cm}^2$  at  $V_G - V_{FB} = -1$  V for the HfSiON [Hf/(Hf+Si)=50%] with an EOT of 5.2 Å. Its leakage current is further reduced to  $4.3 \times 10^{-2}$  A/cm<sup>2</sup> after RTP and deuterium anneal. We believe that the HfSiON film with higher Si content ( $\sim 50\%$ ) and which undergone high temperature annealing at 1050 °C for 60 s has neither crystallization nor interfacial SiO<sub>2</sub> growth as reported earlier.<sup>11</sup> This is due to the film's amorphous nature and high thermal stability at high temperature in the presence of increased Si content. In addition, in Fig. 3, it should be noted that the pure silicon oxide with the PECE

FIG. 3. Current density at a fixed gate bias at  $V_G - V_{FB} = -1$  V as function of the equivalent oxide thickness (EOT) for HfSiON/Si. EOT can be scaled down to 5.2 Å, showing improved scalability. Trend lines for SiO<sub>2</sub>/SiON [Gusev et al. (Ref. 10) and Ref. 13], previous HfSiON data [Sekine et al. (Ref. 9), Gusev et al. (Ref. 10), and Koike et al. (Ref. 8)], and SiO<sub>2</sub> treated by RTP [Chen et al. (Refs. 5 and 6)] are also shown.

effect added exhibits leakage current reduction similar to that of Hf-based high-k oxides at a larger EOT  $(2.2 \text{ nm})^{3}$ ,

The leakage current of the HfSiON gate dielectric is caused by direct tunneling in our case. It was reported that the leakage current depends not only on the film thickness but also on the effective electron mass and/or barrier height of the film.<sup>12</sup> We might suggest that energy coupling might help increase the electron effective mass and energy band gap of the oxide. One might view that the energy band gap is the energy needed to free valence electrons of Si-O bonds. With the enhanced energy coupling, much large energy is needed to free the valence electrons. Thus the corresponding energy band gap might be increased. This might result in a reduction of direct tunneling current.

In summary, we have investigated the effect of phononenergy-coupling enhancement effect on the improvement of leakage current for HfSiON films. The leakage current is reduced by one- and-a- half orders of magnitude after RTP and deuterium annealing of HfSiON gate dielectrics. HfSiON, with the help of the PECE effect, can be scaled down to below 5 Å.

This research is supported by the National Science Foundation (ECS-0093156 and EPS-0447479) and the Office of Vice President for Research, University of Kentucky.

- <sup>1</sup>G. D. Wilk, R. M. Wallace, and J. M. Anthony, J. Appl. Phys. 89, 5243 (2001).

- <sup>2</sup>M. R. Visokay, J. J. Chambers, A. L. P. Rotondaro, A. Shanware, and L. Colombo, Appl. Phys. Lett. 80, 3183 (2002).

- <sup>3</sup>A. Shanware, M. R. Visokay, J. J. Chambers, A. L. P. Rotondaro, J. McPherson, and L. Colombo, Tech. Dig. - Int. Electron Devices Meet. 2003, 939.

- <sup>4</sup>M. A. Quevedo-Lopez, M. El-Bouanani, B. E. Gnade, R. M. Wallace, M. R. Visokay, A. LiFatuo, M. J. Bevan, and L. Colombo, Appl. Phys. Lett. 81, 1074 (2002).

- <sup>5</sup>Z. Chen, J. Guo, and C. B. Samantaray, Proc. 2005 International Semiconductor Device Research Symposium (ISDRS), Washington, DC, 2005, p. 240. <sup>6</sup>Z. Chen, J. Guo, and F. Yang, Appl. Phys. Lett. **88**, 082905 (2006); Z.

Chen and J. Guo, Solid-State Electron. 50, 1004 (2006). Downloaded 18 Oct 2006 to 128.163.42.72. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

- <sup>7</sup>Z. Chen and J. Guo, Proc. 2006 International Reliability Physics Symposium, San Jose, CA, 2006, p. 739.

- <sup>8</sup>M. Koike, T. Ino, Y. Kamimuta, M. Koyama, Y. Kamata, M. Suzuki, Y. Mitani, A. Nishiyama, and Y. Tsunashima, Tech. Dig. Int. Electron Devices Meet. **2003**, 107.

- <sup>9</sup>K. Sekine, S. Inumiya, M. Sato, A. Kaneko, K. Eguchi, and Y. Tsunashima, Tech. Dig. Int. Electron Devices Meet. **2003**, 103.

- <sup>10</sup>E. P. Gusev, D. A. Buchanan, E. Cartier, A. Kumar, D. DiMaria, S. Guha, A. Callegari, S. Zafar, P. C. Jamison, D. A. Neumayer, M. Copel, M. A.

Gribelyuk, H. Okorn-Schmidt, C. Emic, P. Kozlowski, K. Chan, N. Bojarczuk, L.-A. Ragnarsson, P. Ronsheim, K. Rim, R. J. Fleming, A. Mocuta, and A. Ajmera, Tech. Dig. - Int. Electron Devices Meet. **2001**, 451.

- <sup>11</sup>M. A. Quevedo-Lopez, J. J. Chambers, M. R. Visokay, A. Shanware, and L. Colombo, Appl. Phys. Lett. **87**, 012902 (2005).

- <sup>12</sup>Y. Shi, T. P. Ma, S. Prasad, and S. Dhanda, IEEE Trans. Electron Devices 45, 2355 (1998).

<sup>13</sup>2004 ITRS.